1. Overview

SDR-B1 is a software defined radio platform launched by Zencheer, which uses Xilinx Zynq XC7Z045 and ADI AD9363/AD9361. In the original hardware design, the PS of SDR-B1 uses an input clock frequency of 33.333MHz, which is also the input clock frequency used in the reference design. However, recently some customers have proposed the need to use an input clock frequency of 50MHz. This article provides a method to modify the PS input clock frequency. This method is not only applicable to Zencheer SDR-B1, but also to other hardware platforms using Zynq SoC. Since the implementation process of this method is similar to the existing user guidance, this article will not elaborate on the complete process in detail, but only give the key steps. For other details, please refer to "SDR-B1 uses EEPROM to store MAC address".

2. Modify Vivado Project

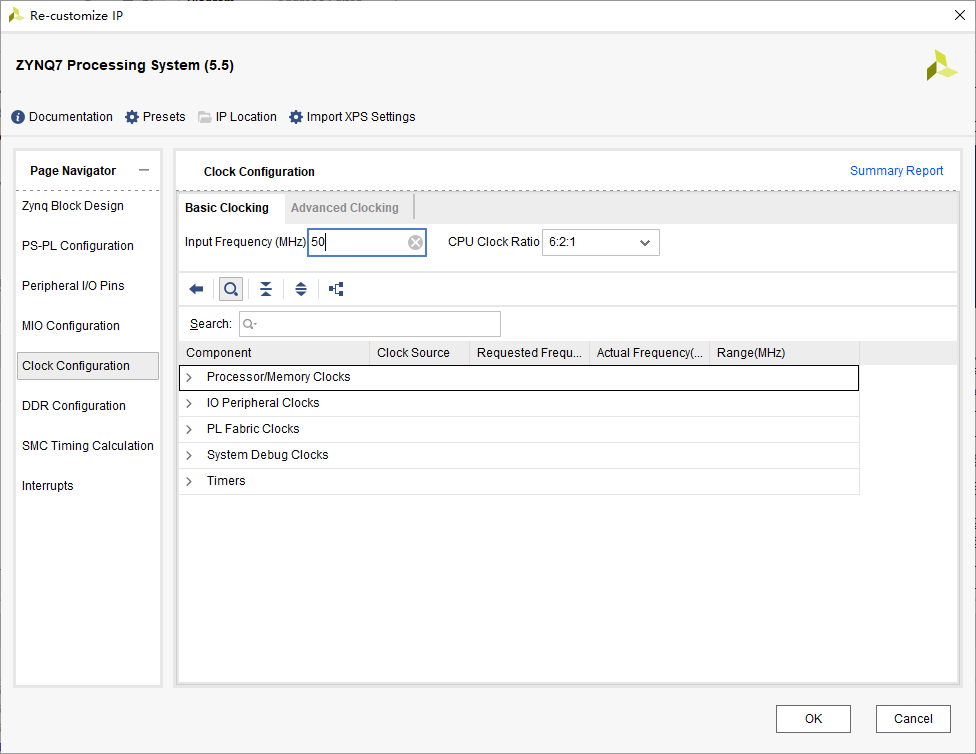

(1) After opening the existing Vivado project, enter the system.bd block diagram, and then double-click ZYNQ to change its input clock frequency to 50MHz, as shown below

(2) Re-Generate Output Products, re-Generate Bitstream, and then copy the obtained system_top.bit and system_top.hdf to Linux for use in the Petalinux project.

3. Modify Linux Code

(1) Modify arch/arm/boot/dts/zynq.dtsi, change ps-clk-frequency to 50000000, and then generate patch 0002-dts-eeprom-and-50mhz-clk-by-zencheer.patch.

(2) Use the previously obtained system_top.bit and system_top.hdf to create a new Petalinux project sdr_b1_v12_50m, and place 0002-dts-eeprom-and-50mhz-clk-by-zencheer.patch in the project-spec/meta-user/recipes-kernel/linux/linux-xlnx/ directory.

(3) Create linux-xlnx_%.bbappend in project-spec/meta-user/recipes-kernel/linux/ and change its content to

SRC_URI_append += "file://0002-dts-eeprom-and-50mhz-clk-by-zencheer.patch"

FILESEXTRAPATHS_prepend := "${THISDIR}/${PN}:"In this way the patch can be applied during kernel compilation.

(4) Use the petalinux-build command to compile and package to obtain BOOT.bin and image.ub. Copy these two files to the TF card and the board can run normally.

4. Precautions

Please note that there is also a zynq.dtsi file in the u-boot source code. In actual tests, modifying the zynq.dtsi under u-boot does not take effect. This can be reflected after turning on the FSBL Debug function. The phenomenon is that the FSBL serial port output is normal, but after entering u-boot, the serial port output is garbled.

Appendix: Enable FSBL Debug in Petalinux

Modify project-spec/meta-plnx-generated/recipes-bsp/fsbl/fsbl_%.bbappend, add the following content

XSCTH_BUILD_DEBUG = "1"Then recompile FSBL using the following command

petalinux-build -c fsbl -x distclean

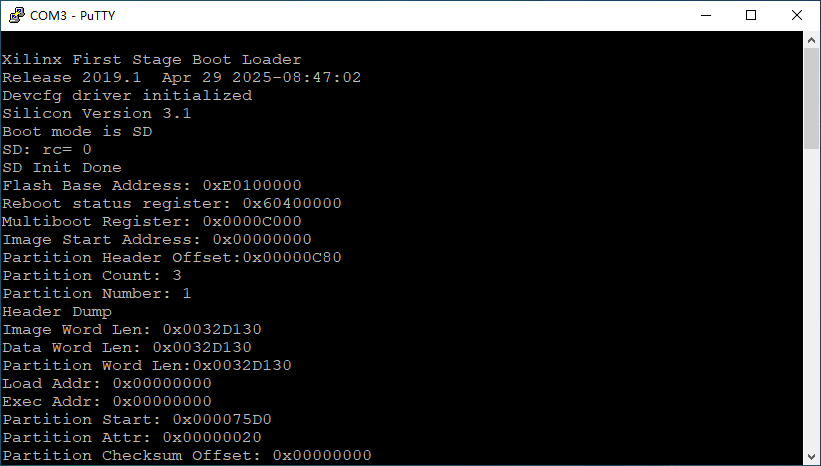

petalinux-build -c fsblPackage BOOT.bin and image.ub again, copy them to the TF card, and then start the board to get the Debug information of FSBL, as shown below